近日,清华大学微电子所、未来芯片技术高精尖创新中心,信息国家研究中心钱鹤、吴华强教授团队与合作者在《自然》在线发表了题为“Fully hardware-implemented memristor convolutional neural network”的研究论文,报道了基于忆阻器阵列芯片卷积网络的完整硬件实现。该成果所研发的基于多个忆阻器阵列的存算一体系统,在处理卷积神经网络(CNN)时的能效比图形处理器芯片(GPU)高两个数量级,大幅提升了计算设备的算力,成功实现了以更小的功耗和更低的硬件成本完成复杂的计算。

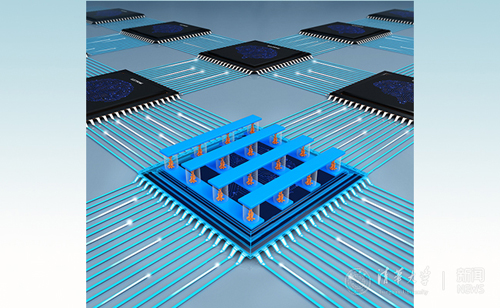

个忆阻器阵列芯片协同工作示意图。基于忆阻器阵列可以实现基于物理定律(欧姆定律和基尔霍夫定律)的并行计算,同时实现存储与计算一体化,突破传统架构对算力的限制。

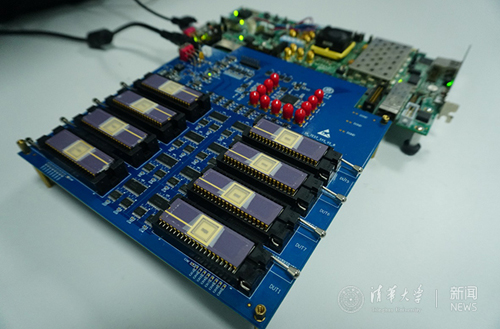

基于忆阻器芯片的存算一体系统

随着人工智能应用对计算和存储需求的不断提升,集成电路芯片技术面临诸多新的挑战。一方面,随着摩尔定律放缓,通过集成电路工艺微缩的方式获得算力提升越来越难,另一方面,在传统架构中,计算与存储在不同电路单元中完成,会造成大量数据搬运的功耗增加和额外延迟。阿里达摩院在2020年1月发布了《2020十大科技趋势》报告,其中第二大趋势为“计算存储一体化突破AI算力瓶颈”。报告指出:“数据存储单元和计算单元融合为一体,能显著减少数据搬运,极大提高计算并行度和能效。计算存储一体化在硬件架构方面的革新,将突破AI算力瓶颈”。基于忆阻器的新型存算一体架构可以利用欧姆定律和基尔霍夫电流定律的实现基于物理定律的原位计算(Compute on Physics),打破传统架构中的算力瓶颈问题,满足人工智能等复杂任务对计算硬件的高需求。

当前国际上的相关研究还停留在简单网络结构的验证,或者基于少量器件数据进行的仿真,基于忆阻器阵列的完整硬件实现仍然有很多挑战:器件方面,制备高一致、可靠的多值忆阻器阵列仍是挑战;系统方面,受忆阻器的阻变机理制约,器件固有的非理想特性(如器件间波动,器件电导卡滞,电导状态漂移等)会导致计算准确率降低;架构方面,忆阻器阵列实现卷积功能需要以串行滑动的方式连续采样、计算多个输入块,无法匹配全连接结构的计算效率。

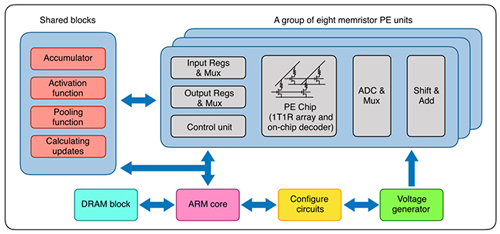

钱鹤、吴华强教授团队通过优化材料和器件结构,成功制备出了高性能的忆阻器阵列。为解决器件非理想特性造成的系统识别准确率下降问题,提出一种新型的混合训练算法,仅需用较少的图像样本训练神经网络,并通过微调最后一层网络的部分权重,使存算一体架构在手写数字集上的识别准确率达到96.19%,与软件的识别准确率相当。与此同时,提出了空间并行的机制,将相同卷积核编程到多组忆阻器阵列中,各组忆阻器阵列可并行处理不同的卷积输入块,提高并行度来加速卷积计算。在此基础上,该团队搭建了全硬件构成的完整存算一体系统,在系统里集成了多个忆阻器阵列,并在该系统上高效运行了卷积神经网络算法,成功验证了图像识别功能,证明了存算一体架构全硬件实现的可行性。

存算一体系统架构

近年来,钱鹤、吴华强教授团队长期致力于面向人工智能的存算一体技术研究,从器件性能优化、工艺集成、电路设计及架构与算法等多层次实现创新突破,先后在《自然通讯》(Nature Communications)、《自然电子》(Nature Electronics)、《先进材料》(Advanced Materials)等期刊以及国际电子器件会议 (IEDM)、国际固态半导体电路大会(ISSCC)等顶级学术会议上发表多篇论文。

团队合影

吴华强教授是本论文的通讯作者,清华大学微电子所博士生姚鹏是第一作者。该研究工作得到了国家自然科学基金委、国家重点研发计划、北京市科委、北京信息科学与技术国家研究中心及华为技术有限公司等支持。

文章链接:

https://www.nature.com/articles/s41586-020-1942-4